Introduction

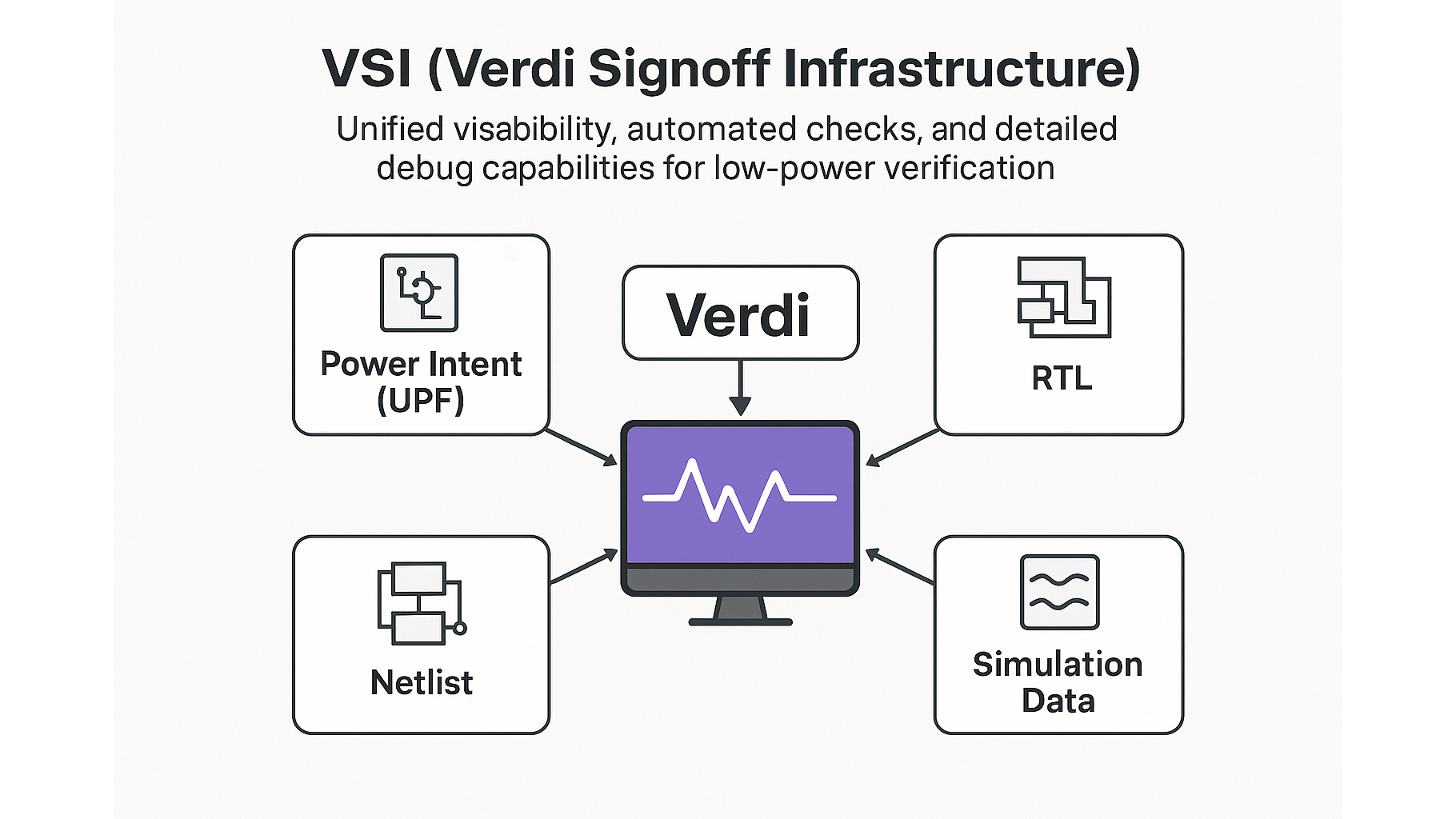

VSI (Verdi Signoff Infrastructure) is a structured, signoff-driven verification methodology built around Synopsys Verdi. It provides unified visibility, automated checks, and detailed debug capabilities for low-power verification.

VSI integrates power intent (UPF), RTL, netlist, and simulation data into a single flow to ensure that every low-power strategy is correctly implemented and thoroughly verified before tape-out.

Why Low-Power VSI Is Important

As chips become smaller and more complex, issues such as improper isolation control, incorrect retention behavior, or illegal power sequencing can lead to X-propagation, functional corruption, or even silicon failure.

VSI ensures that:

- The UPF intent is interpreted accurately

- All low-power cells (isolation, retention, level shifters, power switches) are implemented correctly

- Power state transitions behave as expected during simulation

- Coverage requirements for low-power scenarios are fully met

- Debug of power-aware issues is fast, visual, and efficient

Core Low-Power Concepts Verified Through VSI

1. Power Domains and Power States

Designs are divided into multiple power domains that can turn ON/OFF independently.

VSI checks domain definitions, legality of power modes, and all transitions defined in the Power State Table (PST).

2. Isolation Strategies

When a domain powers down, isolation cells prevent unknown values (X) from propagating into active domains.

VSI ensures isolation control signals, polarity, and placement match UPF intent.

3. Retention Strategies

Retention registers preserve essential state during shutdown.

VSI validates correct save/restore sequences, mapping, and coverage of retention events.

4. Level Shifting

Voltage differences between domains require level shifters.

VSI checks their presence, direction, and consistency.

5. Power Sequencing

Power-down and power-up sequences must follow strict protocols.

VSI analyzes waveform behavior to confirm legal transitions and detect violations.

VCLP: The Engine Behind VSI Low-Power Debug

VCLP (Verdi Common Low-Power) is the core technology that enables:

- UPF-aware waveform debugging

- Dynamic low-power simulation analysis

- Cross-probing between RTL, Netlist, UPF, and waveforms

- Visualization of domain states, isolation behavior, retention activity, and X-propagation

It bridges static and dynamic checks to provide a true signoff-quality view of the design’s low-power behavior.

What VSI Guarantees for Low-Power Signoff

A design is considered ready for low-power signoff when:

- All static UPF checks are clean

- All power states and transitions are simulated and covered

- No illegal X-propagation is observed

- Isolation, retention, and level shifter behavior is verified

- Power sequencing matches the architectural intent

- All UPF rules are implemented and validated in both RTL and gate-level flows

- Debug traces show correct domain and voltage behavior

- All must-fix issues are resolved with documented waivers

Conclusion

In modern advanced-node designs, low-power verification is no longer optional—it is a critical path to silicon success.

VSI, powered by VCLP, provides a comprehensive framework that aligns UPF intent, RTL design, and simulation behavior into a unified signoff methodology. By ensuring complete and correct verification of low-power strategies, VSI helps teams achieve reliable, efficient, first-time-right silicon